TEST GENERATION FOR SYSTEM-ON-CHIP SECURITY VALIDATION By YANGDI LYU A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL OF THE UNIV

PDF) Improving Datapath Testability by Modifying Controller Specification | Marie-lise Flottes - Academia.edu

High-Level Approaches to Hardware Security: A Tutorial | ACM Transactions on Embedded Computing Systems

Practical fault resilient hardware implementations of AES - Sheikhpour - 2019 - IET Circuits, Devices & Systems - Wiley Online Library

Atelier HLP - Photos d'enfance - Parcours Education Artistique et Culturelle (PEAC) - LYCEE THEOPHILE ROUSSEL

a) Chemical structure and CPK (Corey – Pauling – Koltun) model of the... | Download Scientific Diagram

Practical fault resilient hardware implementations of AES - Sheikhpour - 2019 - IET Circuits, Devices & Systems - Wiley Online Library

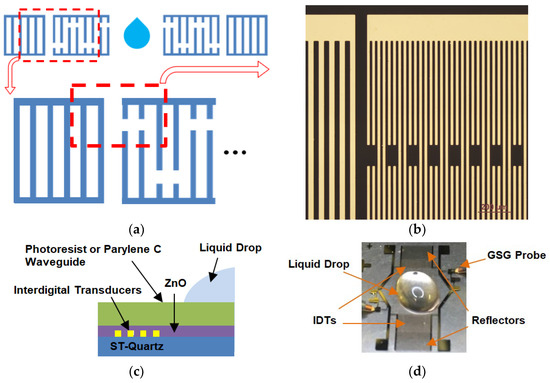

Sensors | Free Full-Text | Liquid Viscosity Sensor Using a Surface Acoustic Wave Device for Medical Applications Including Blood and Plasma

Hardware obfuscation of AES IP core using combinational hardware Trojan circuit for secure data transmission in IoT applications - Chhabra - 2022 - Concurrency and Computation: Practice and Experience - Wiley Online Library

Contactless pre-bond TSV fault diagnosis using duty-cycle detectors and ring oscillators | Semantic Scholar

![PDF] Parity-Based Concurrent Error Detection Schemes for the ChaCha Stream Cipher | Semantic Scholar PDF] Parity-Based Concurrent Error Detection Schemes for the ChaCha Stream Cipher | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/1f4bd3d0625e25e81f4ba75cc0b1237ea7c11e46/2-Figure1-1.png)